## **Gryphon PCM**

## Complete Rackmount 40 Mbps Dual PCM Prosessing System

Dual Bit Sync/Dual Frame Sync/Frame Archiver/IRIG Time Code Reader/PCM Baseband Simulator with Optional Dual PCM Decommutator Chapter 10 Storage/Ethernet Transmission/BERT/Baseband Functionality

Where Technology Soars

A Woman-Owned Small Business

www.ulyssix.com

**Gryphon PCM**

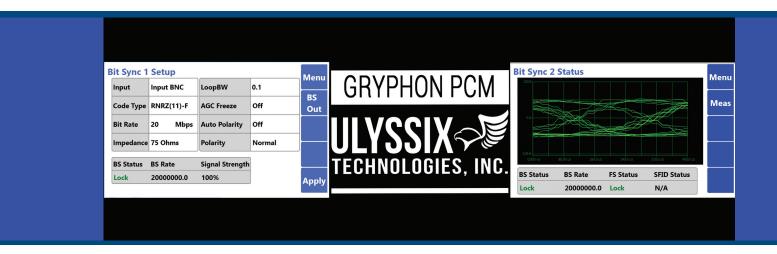

Ulyssix's Gryphon PCM 2U rackmount is complete baseband, ground-based telemetry system. The Gryphon PCM system uses the combined advanced 3rd generation Tarsus3-PCIe-02 with an embedded processor. The full functionality of the Ulyssix solution gives the user complete baseband data acquisition with data processing in this single solution. The Gryphon PCM is set up and controlled by dual high-resolution color HDMI touchscreen displays for complete flexibility using the front panel touchscreen interface. The Gryphon PCM solution is powered by the latest INTEL/Altera FPGA technology with user upgradable DSP firmware algorithms.

Gryphon PCM 2U Dual Bit/ Frame Sync System

| Input     | Input RX   | LoopBW        | 0.1    | Menu |

|-----------|------------|---------------|--------|------|

| Code Type | RNRZ(11)-F | AGC Freeze    |        | Rx   |

| Bit Rate  | 20 Mbps    | Auto Polarity | Off    | FS   |

| Impedance | 75 Ohms    | Polarity      | Normal |      |

| BS Status | BS Rate    |               |        |      |

| Lock      | 20000000.0 |               |        |      |

| Frame Sync 1 Setup |           |                |           | — Menu |

|--------------------|-----------|----------------|-----------|--------|

| Bits per MF        | 256       | Sync Errors    | o         | Wiellu |

| FS Pattern Bits    | 32        | Bit Slips      | 0         | SubFS  |

| FS Pattern         | fe6b2840  | Burst Mode     | Off       | BS     |

| FS Mask            | o         | Data In Search | Off       |        |

| Number MF          | 64        |                |           | Sim    |

| Frame Lock         | SFID Lock | SFID           | Bit Slips |        |

| Lock               | Lock      | 48             | 0         |        |

#### Bit Synchronizer

Designed using all DSP filter algorithms in FPGA technology for maximum performance capability

Accepts all IRIG 106 PCM code types

Bit Sync programmable input rates from 1 bps to 40 Mbps

Less than 1 dB to theoretical bit sync BER performance

Integrated graphic eye pattern display for complete lock indication

#### Frame Synchronizer

Supports PCM streams from 1 bps up to 50 Mbps

Supports up to 1024 minor frames per major frame and 16 M bits per minor frame

Frame Sync Archive capability

Advanced algorithm to allow for varying frame sizes

Input either from bit sync or external clock and data

## Storage & Diagnostics

Diagnostic feature used to aid Ulyssix in troubleshooting FPGA firmware internal control register configuration from user setup configuration

Retrieval popup form in GRYPHON software suites outputs diagnostic file for transfer to Ulyssix for quick system analysis for card configuration errors, setup errors or actual hardware failures

The Gryphon PCM Tarsus3 PCM processor board is powered by the latest INTEL/ALTERA ArriaV GZ and Cyclone III FPGA's. The firmware is user reconfigurable using the Gryphon PCM software suite with user upgradable capability when under maintenance contract. Using optional Chapter 10 Ethernet or UDP Parameter/Broadcast software, the Gryphon PCM system can be used for remote monitoring of time tagged frame lock PCM data.

## Gryphon PCM Features:

Features Included: Dual Multi-Mode Receivers Dual PCM Baseband IRIG Time Code Reader PCM Simulator Setup

#### **Optional Features:**

RF Modulating Generator

IRIG CH10 Recorder/Playback

UDP Frame and Parameter

Broadcasting

Internal BERT Operation

Dual Decommutator

Viterbi Decoder

#### IRIG Time Code Reader

IRIG Time interpolated to 1 usec

Supports DC Level IRIG-B and AM

Modulated IRIG A, B, G & NASA-36

Used for both IRIG time display

and/or minor frame time tag

header information

resolution

#### PCM Simulator

Programmable PCM streams from 1 bps up to 40 Mbps

Ulyssix .tad frame sync file and Chapter 10 Archive playback capability

Fixed major frame simulator utilizing defined waveform & tabular data to output

Convolutional Encoder output capable for Viterbi Simulator

Selectable output code type

TTL and RS422 output capability

Optional TPC Encoder capability

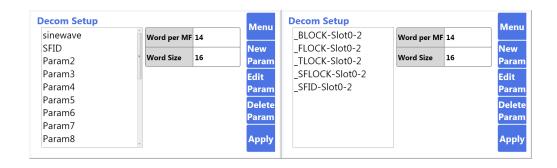

### Optional Decommutator

Supports all IRIG Class II decommutator features with variable word length from 3 - 64 bits, format switching, parameter concatenation and asynchronous embedded formats

High speed data transfer of user word selected channels to the PCI bus for disk storage and playback

Two on card DACs for word analog output

Full parameter math processing

Available with two different user friendly Windows GUI based software suites for full setup of format frame, word selection, channel display capability and optional client/server capability

#### Where Technology Soars

# Gryphon PCM

|                                                 |                                                                                                                                                   | if. a a + i a la a                 | *                                                                                                                                   |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| PUM Pro                                         | ocessor Spec                                                                                                                                      | cincations                         |                                                                                                                                     |

|                                                 |                                                                                                                                                   |                                    |                                                                                                                                     |

| Bit Synchronizer Input Specifications           |                                                                                                                                                   | PCM Simulator Specifications       |                                                                                                                                     |

| Input Data Rate                                 | Bit Sync programmable input tunable rates from 1 bps to 40 Mbps for NRZ-L/M/S, RNRZ-L, and 1                                                      | Output Data Rate                   | 1 bps to 40 Mbps for NRZ-x, RNRZ-L, or 20 Mbps for all others                                                                       |

| Input Source                                    | bps to 20 Mbps for Bi-Φ L/M/S  2 independent inputs (1 single ended BNC, 1 differential Twinax)                                                   | Output PCM Codetypes               | NRZ-L/M/S, RNRZ-L 11/15, RZ, Bi-Φ L/M/S,<br>RNRZ 11/15/, forward/reverse, program<br>selectable                                     |

| Input Impedance                                 | Hi-Z/75Ω/50Ω, single ended input, software                                                                                                        | Output Signal Levels               | Data and Clock, TTL, and RS422 level driven                                                                                         |

|                                                 | selectable, BNC input, 120 ohms Differential                                                                                                      | Word Lengths                       | 3 to 64 bits, variable length                                                                                                       |

| Maximum Safe Input                              | ± 35 VDC                                                                                                                                          | Frame Length                       | Same as decommutator specs                                                                                                          |

| Input Signal Level                              | 30 mVp-p to 5 Vp-p                                                                                                                                | Data Words                         | Fixed or math functions (sine wave, triangle,                                                                                       |

| DC Input Level                                  | +/- 5 VDC                                                                                                                                         | Data Tronsc                        | square wave, sawtooth, counter) with                                                                                                |

| Input PCM Codetypes Modes                       | NRZ-L/M/S, RNRZ-L, RZ, Bi-Φ L/M/S, program selectable (consult factory for other codetypes)                                                       | Time of the Decider Once           | programmable sample rate                                                                                                            |

| Derandomizer Input                              | RNRZ-11/15, forward/reverse, program                                                                                                              | Time Code Reader Specifications    |                                                                                                                                     |

|                                                 | selectable                                                                                                                                        | IRIG Codetypes                     | DC Level IRIG-B and AM Modulated IRIG A, B, G, & NASA-36                                                                            |

| Input Polarity                                  | Normal, inverted, or auto selectable using frame<br>sync correlator                                                                               | Gryphon PCM Diagnostics            |                                                                                                                                     |

| Bit Synchronizer Data Specifications            |                                                                                                                                                   | Version Control                    | All current software, firmware and driver version numbers stored for easy retrieval                                                 |

| Loop Bandwidth                                  | 0.01% to 3.0%, to the programmed bit rate                                                                                                         | Latest Setup                       | Current card setup configuration is stored for                                                                                      |

| Capture Range                                   | +/-3 times of the programmed loop bandwidth                                                                                                       |                                    | verification of proper setup                                                                                                        |

| Data Tracking Range                             | +/-5 times of the programmed loop bandwidth                                                                                                       | Diagnostic Download                | Direct download to file for transfer to Ulyssix for                                                                                 |

| Sync Acquisition                                | Less than 200 bits, typically 100 bits max                                                                                                        | DI : 10 :C ::                      | evaluation and recommendations                                                                                                      |

| Bit Error Probability                           | Less than 1 dB to theoretical bit sync BER per-<br>formance for bit rates up to 25 Mbps, less than 2<br>dB to theoretical from 25 Mbps to 40 Mbps | Physical Specifications Dimensions | 2U 19" rackmount chassis with 100V-240V AC input capability                                                                         |

| Bity Sync Output                                | TTL and RS422 Level driven                                                                                                                        | Interface Connectors               | Baseband PCM inputs and outputs through single ended 75 ohm BNC rackmount connectors & Differential Twinax                          |

| Bit Sync Code Types                             | NRZ-L/M/S, RNRZ-L, RZ, Bi-Φ L/M/S, or RNRZ<br>11/15, program selectable                                                                           | co.raco commentoro                 |                                                                                                                                     |

| Clock Output                                    | 0°, 90°, 180°, 270°                                                                                                                               | Manufacturing                      | The design utilizes Surface Mount Technology (SMT), manufactured with robotic assembly techniques to IPC-610B Class 2 manufacturing |

|                                                 |                                                                                                                                                   |                                    |                                                                                                                                     |

| Frame Sync/Optional Decommutator Specifications |                                                                                                                                                   |                                    | standards                                                                                                                           |

| Input Data Rate                                 | Up to 50 Mbps                                                                                                                                     | Temperature Range                  | Operating: 0°C to 50°C                                                                                                              |

| Input Signals                                   |                                                                                                                                                   |                                    | Storage: -20°C to 60°C<br>Less than 300 Watts                                                                                       |

| , J                                             | direct from Bit Sync section of the PCM<br>Processor, NRZ-L and clock                                                                             | Power Consumption Ordering Options | Less than 300 watts                                                                                                                 |

| Word Lengths                                    | 3 to 64 bits variable from channel to channel                                                                                                     | Gryphon-PCM                        | 2U rackmount Dual, Dual PCM Processing                                                                                              |

| Minor Frame Length                              | 3 to 16,777,216 bits                                                                                                                              | өтургіоп-Рсіхі                     | capability, IRIG Time Code Reader, PCM                                                                                              |

| Major Frame Length                              | 1 to 1024 minor frames per major frame                                                                                                            |                                    | Simulation and BERT Tester Option for Bit Error                                                                                     |

| PCM bit word order                              | MSB or LSB, word by word basis, program selectable                                                                                                | ULX-OPT-CH10                       | Tester of RF and PCM Data Stream Chapter 10 recording and reproducer for both                                                       |

| Frame Sync Pattern                              | 16 to 64 bits                                                                                                                                     |                                    | Chapter 10 disk files and UDP-CH10-Ethernet packets                                                                                 |

|                                                 |                                                                                                                                                   |                                    | paoneto                                                                                                                             |

ULX-OPT-Viterbi

#### Frame Sync Location Leading the minor frame Frame Sync Strategy Search-Check-Lock, programmable counts per Subframe Sync FCC or SFID Sync Error Tolerance 0 to 8 bits, program selectable Bit Slip Window 0 to 9999 bits, program selectable Data Polarity Normal or inverted on a channel by channel Asynchronously Supports up 8 asynchronous embedded formats **Embedded Formats** based on computer CPU capability Bit Concatenation/Fragmented Software decommutator can combine individual bits from separate PCM words Words **DAC Output Specifications**

| Manufacturing                        | The design utilizes Surface Mount Technology (SMT), manufactured with robotic assembly techniques to IPC-610B Class 2 manufacturing standards                           |  |  |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Temperature Range                    | Operating: 0°C to 50°C<br>Storage: -20°C to 60°C                                                                                                                        |  |  |

| Power Consumption                    | Less than 300 Watts                                                                                                                                                     |  |  |

| Ordering Options                     |                                                                                                                                                                         |  |  |

| Gryphon-PCM                          | 2U rackmount Dual, Dual PCM Processing<br>capability, IRIG Time Code Reader, PCM<br>Simulation and BERT Tester Option for Bit Error<br>Tester of RF and PCM Data Stream |  |  |

| ULX-OPT-CH10                         | Chapter 10 recording and reproducer for both<br>Chapter 10 disk files and UDP-CH10-Ethernet<br>packets                                                                  |  |  |

| ULX-OPT - Dual Decom                 | Optional Word Selector with Graphic Displays for Individual Decom Parameter Procession                                                                                  |  |  |

| ULX-OPT-IRIGTIMEOUT                  | Optional IRIG Time output from .tad archive file playback                                                                                                               |  |  |

| ULX-OPT-LQTESTER                     | BERT Tester Option for Time Latency<br>Measurements and Bit Error Tester of PCM Data<br>Stream                                                                          |  |  |

| ULX-OPT-RTSIM                        | Optional real-time simulator parameter variability. Used to change parameters while running simulator                                                                   |  |  |

| ULX-OPT-TPC                          | Optional Turbo Product Code (TPC) encoding and decoding                                                                                                                 |  |  |

| ULX-OPT-UDP PARAM/FRAME<br>BROADCAST | UDP Frame and/or decom parameter multicast or unicast broadcast for external ALTAIR software networking or external data transfer                                       |  |  |

1 Vpp to 5 Vpp, selectable in 0.1 Vpp steps,  $\pm$

2.5V offset in 0.1 VDC steps

Number of Channels

Output Level

Viterbi decoding solution