# USING ASICS TO IMPLEMENT A PROGRAMMABLE DIGITAL FM DEMODULATOR

**Glenn K. Rosenthal**

Metraplex Corporation Frederick, MD 21701

### ABSTRACT

With the advancement in speed and complexity of Application Specific Integrated Circuits (ASICs), Digital Signal Processing (DSP) algorithms can now be used to achieve fully programmable, multiple channel demodulation of Frequency Modulation (FM) multiplexes. This paper describes the DSP algorithms and ASIC implementation used in the design of a digital FM demodulator system. Each digital demodulator has programmable subcarrier frequency demodulation to 4 MHz, programmable digital output filtering, and tape speed compensation (TSC). The demodulator output is available in both digital form for direct computer interface and in analog form for conventional analysis.

### **KEY WORDS**

FIR Filtering, Decimation Filtering, Oversample Filtering, Digital Signal Processing

### INTRODUCTION

Analog wide-band FM multiplexing and demultiplexing systems have been used extensively by the data acquisition and telemetry community for measuring high-frequency data. Wide-band analog tape recorders are still the most efficient way to store data.

The problem with analog FM instrumentation has always been that it lacks programmability, requires frequent and lengthy calibration, and continually drifts with time and temperature. Although digital data measurement techniques, such as digitization and pulse code modulation (PCM), solve some of problems, they have had only limited success for wide-band applications. The high data rates require enormous digital storage capacity and are still a major technological barrier. DSP algorithms implemented using new ASIC technology can perform all the multiplexing, demultiplexing, and filtering functions needed to create a digital FM system, including the benefits of full programmability, crystal accuracy and stability, and calibration-free operation.

#### SYSTEM DESIGN FEATURES

The central design goal for the digital FM demodulator is to give the user all the standard features expected in an analog demodulator, and then make it completely programmable and calibration-free.

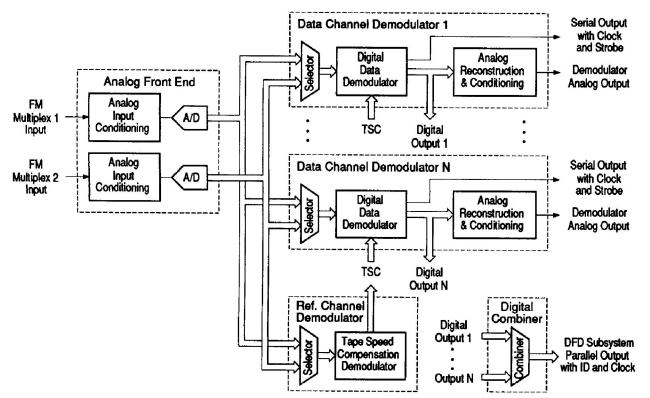

The result is the Digital Frequency Demultiplexes (DFD) system shown in Figure 1. Utilizing a fully programmable, DSP implemented design approach, the DFD system directly replaces existing wideband analog FM demultiplexing systems. The architecture of the DFD is similar to its analog counterpart and includes a front end section, data demodulators, and a TSC reference demodulator. However, the DSP implementation provides numerous advantages over the conventional analog system.

Figure 1. DFD System Architecture

Conventional plug-in analog FM demodulators use analog pulse-averaging demodulators that are prone to drift. They also rely on passive fixed-frequency filters for channel selection and output filtering. In contrast, the digital FM demodulators are

fully programmable and can perform the entire demodulation process using programmable DSP algorithms.

The DFD assures frequency accuracy by implementing a synchronous digital pipeline design based on one extremely stable clock oscillator. Because the DFD employs a synchronous digital pipeline design, all demodulator outputs are time correlated, thereby eliminating the effects of bandwidth dependent propagation delay as well as time and temperature drift.

Each digital demodulator operates independently and employs identical DSP algorithm circuitry for identical programmability and complete interchangeability. Each demodulator is independently programmable for a subcarrier frequency from 256 Hz to 4 MHz and deviation range from 6 Hz to 500 kHz. Each demodulator also provides programmable output filtering to achieve subcarrier/data deviation ratios from 1 to 512 without any degradation in the signal-to-noise performance — something not possible in an analog design.

With a 4 MHz input bandwidth capability, the DFD can handle FM multiplex inputs from the new 4 MHz analog tape recorders as well as real-time inputs from conventional multiplexers and the DSP implemented Digital Frequency Multiplexer (DFM) system.

For data analysis, there is no need to add a separate digitizing system to the output of the demodulator. In addition to the analog outputs (for stripchart and oscilloscope capability), the DFD provides digital outputs (data, ID, and clock) for direct interface with data reduction computer systems or for storage on digital tape recorders.

The physical dimensions of the DFD are similar to existing analog FM demultiplexing systems. The DFD is 8.75 inches high and fits in a 19-inch wide rackmount housing. Each DFD provides two 4 MHz analog FM multiplex inputs, up to 20 independent digital data demodulators (packaged two per card), two tape speed compensation demodulators that can also be used as data demodulators, and a parallel digital output. A microcontroller in each DFD programs the hardware and handles the user interface. The DFD system is expandable by adding up to 13 slave DFD subsystems, all controlled from one of three sources: locally via the master DFD's electroluminescent (EL) graphic display with infra-red touch screen user interface, or remotely either by an IBM-PC compatible computer or a by a host computer system using GPIB or RS-232 computer interface.

### **DESIGN IMPLEMENTATION DESCRIPTION**

The DFD design implementation (Figure 1) is divided into four sections:

- 1. Analog front end to signal condition and digitize the FM multiplex input.

- 2. Data channel digital demodulators to provide digital data outputs.

- 3. Analog reconstruction and conditioning to provide analog outputs.

- 4. Digital data combiner to provide the parallel data output.

Each of these sections is designed to be completely programmable, in contrast to the analog approach of turning potentiometers, setting switches, or changing plug-in modules.

### **Analog Front End**

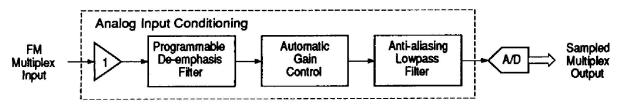

The analog front end section provides identical circuitry for processing two analog FM multiplexes with bandwidths up to 4 MHz. Each multiplex is independently signal conditioned and then digitized to provide a sampled output at 16 MHz. Each demodulator includes a programmable input selector for choosing the desired multiplex. Figure 2 shows the front end processing for one multiplex.

An input amplifier buffers the FM multiplex input and feeds it to a user programmable de-emphasis filter, which is programmable from 1 kHz to 1 MHz. This one-pole filter allows the user to shape the amplitude taper of the multiplex input spectrum to correct for the pre-emphasis performed on the FM multiplex prior to recording on tape. The de-emphasized filter output is a multiplex spectrum with uniform amplitude level, which greatly improves the signal-to-noise performance of all channels prior to digitization.

Next, an automatic gain control (AGC) circuit adjusts the overall amplitude of the data to achieve the highest signal resolution prior to digitizing the multiplex. The AGC is designed to provide constant output levels for inputs from 2 mV to 2 V rms.

The anti-aliasing lowpass filter eliminates any frequency terms in the multiplex above 4 MHz. This passive filter provides pre-sample filtering to keep the signal spectrum below the Nyquist rate of the digital data pipeline in the demodulators.

Lastly, the analog input data is digitized using a 12-bit sampling analog-to-digital (A/D) converter at a rate of approximately 16 MHz. By sampling at 4 times the highest input frequency, all multiplex data can be digitized together, thus eliminating the need for programmable anti-aliasing filters. Any remaining unwanted frequencies in the digitized multiplex are digitally filtered out by the digital data demodulator.

## **Digital Data Demodulators**

Each data channel demodulator contains a digital data demodulator providing a digital output, followed by a reconstruction and conditioning circuit for converting the digital output to an analog output.

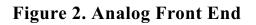

The heart of the DFD is the individual digital data demodulator. The FM demodulation process is a series of DSP hardware mathematic algorithm blocks (Figure 3). Because of the extremely high bandwidth of the input data, standard DSP processors (e.g., Texas Instruments TMS320 or Analog Devices 21xx) can not perform the computations fast enough. The DFD uses both Metraplex proprietary ASICs and industry supplied Very Large Scale Integrated (VLSI) modules to implement the DSP functions.

Figure 3. Digital Data Demodulator

The reason the DFD has such a wide programmable range for each of its data demodulators is the use of independent, ASIC implemented, filter modules for each channel. ASIC gate array technology allows each filter module to be cost effective as well as efficiently packaged. Metraplex developed two new DSP algorithm ASICs for the DFD design, which are joined by previously developed ASICs from the DFM design. Both new ASICs are digital filter modules performing Finite Impulse Response (FIR) algorithms. The first ASIC is a unique decimation filter module and the second ASIC is an oversampling filter module. By creating these fully synchronous DSP filter modules, no circuitry has to be time-shared between channels. This allows the DFD to have essentially perfect time correlation between demodulator channel outputs in the multiplex.

The digital data demodulator design approach in Figure 3 starts with a complex frequency translation of the desired input channel. This translates the desired channel center frequency down to where the demodulated output is centered around DC or 0 Hz. The classical deviation bandpass filter is eliminated because the desired channel can be extracted from the translated multiplex using a digital lowpass filter.

The complex frequency translation is performed using a Metraplex developed ASIC. The ASIC is programmed to the center frequency of the desired channel and generates two waveforms in perfect quadrature (sine and cosine). The digitized FM multiplex is then multiplied by both the real (sine) and imaginary (cosine) portions of the waveform to produce the sum and difference frequency terms of the multiplex with respect to the user programmed center frequency. Since both the real and imaginary data travel through the ASIC pipelines in parallel, there are an identical number of register delays in each path to maintain perfect time correlation of the two waveforms.

The next stage the demodulator eliminates all unwanted sum and difference frequency terms from the frequency translated multiplex. The first stage of this digital filtering process is the decimation filter, which passes only the data from DC to one-half the Nyquist sample rate. In order to meet the desired wide-band frequency response for each demodulator, a multiple half-band decimation FIR filter was implemented in the Metraplex ASIC. According to the Nyquist sampling theorem, the output of a half-band decimation filter can be resampled at half the original rate without losing any information and causing any aliasing of the input data.

The ASIC decimation filter allows the output decimated data to be fed back into the same half-band filter to be further decimated. This is accomplished by designing the ASIC so that the calculation of the first decimation process takes less than half the decimated sample time. The other half of the available time is used to process a decimation filtering of a higher order. The partial decimation filtered values are stored within the ASIC and controlled by a state machine that determines the appropriate time slot to feedback the partial decimation filter value. The total number of decimations depends on the programmed deviation bandwidth of the channel being demodulated. The decimation filter serves as a preliminary deviation lowpass filter stage, but more importantly, it slows down the digital pipeline clock to allow use of a precision FIR filter as a deviation input filter.

Tape speed compensation (TSC) may be applied to the decimated data prior to the input filter. The output of the TSC demodulator (which is identical to a data demodulator) is used to frequency shift the data demodulator output to compensate for variations in the tape speed during playback of the analog tape recorder. This process is performed using standard VLSI multiplying modules.

Now the real and imaginary pipeline digital data are prepared for the final stage of the deviation input filter. The final stage is another FIR filter with a programmable lowpass cutoff frequency. The DFD microcontroller calculates the filter coefficients using a modified Remez Exchange algorithm from the user entered deviation bandwidth data, and then downloads the filter coefficients to the demodulator hardware. The FIR input filter uses a multiply accumulator VLSI module to perform the digital filtering. The input filter coefficients are optimized to prevent harmonic distortion terms from increasing as the deviation ratio is reduced to one. This is not possible with traditional analog bandpass input filters.

After the input filter, the data passes through a frequency-to-phase converter and then through a phase-to-amplitude converter. The first uses the ratio of the real and imaginary filtered data to convert from the frequency domain to the phase domain by comparing the phase relationship of the quadrature terms. The second converts data from phase domain to the amplitude domain by multiplying the digital data by a scalar value calculated from the user programmed deviation of the channel. Final TSC gain correction is performed on the deviation scalar prior to multiplying the scalar against the phase data.

Finally, the digital pipeline data passes through a digital output filter consisting of another Metraplex decimation filter ASIC and user programmable FIR filter. The decimation filter allows the user to program deviation ratios from 1 to 512. Again, the pipeline data with be decimated to a rate where the output FIR filter can have maximum performance.

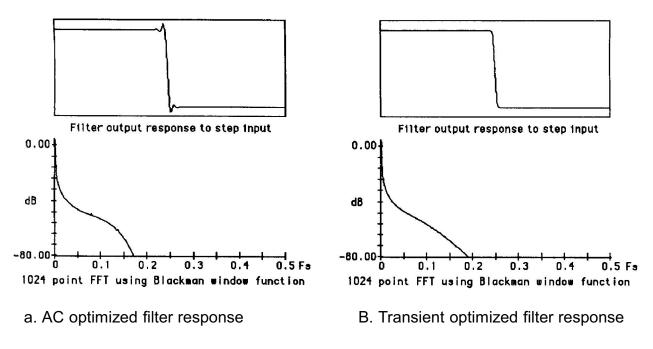

The user has the choice of two different modes of response for the digital output filter (Figure 4). Both modes are FIR constant amplitude, constant delay digital filters. The coefficients for one filter mode are optimized for AC performance and provide a response that is -0.1 dB at cutoff and -60.0 dB at 2.0 times cutoff. This filter mode removes all distortion terms generated in the frequency to amplitude conversion.

The coefficients for the other filter mode are optimized for transient or step response performance and provide a response that is -3.0 dB at cutoff and -60 dB at 2.5 to 3.0 times cutoff. This filter mode removes the unwanted overshoot terms on step response

input data. The DFD microcontroller calculates the coefficients for the desired output filter mode and downloads them to the demodulator hardware.

Figure 4. Step Response Comparison of Digital FIR Output Filters

### **Analog Reconstruction and Conditioning**

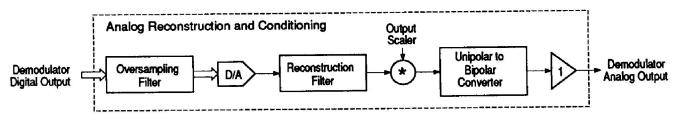

The analog reconstruction process (Figure 5) must accommodate different sample rates. Digital pipeline output filtered data in each digital demodulator may be running at a different sample rate, depending on the number of decimations needed to achieve the required channel deviation and output filtering. In order to avoid designing switchable analog reconstruction filters, Metraplex developed another proprietary ASIC that performs an oversampling or digital interpolation of the pipeline digital data to speed up the sample rate of the digital data pipeline. This oversampling filter is the reverse of the decimation filter. Instead of feeding back each decimation to reduce the number of output samples, the oversampling filter uses interpolation to increase the number of output samples. To perform the different levels of interpolation, the input data is convolved with the appropriate number of coefficients from the same impulse response. This technique allows the amount of interpolation to be directly related to the number of coefficients stored. The DFD oversamples all digital demodulators to obtain the same output sample rate.

Analog reconstruction is performed using a 12-bit, high speed, digital-to-analog (D/A) converter running at a sample rate that is synchronous to the pipeline system clock. A lowpass reconstruction filter after the D/A removes the digital pipeline clock and associated digital sampling terms caused during the analog reconstruction of the

demodulator output. This reconstruction filter has a passband from DC to 500 kHz and covers the entire output frequency bandwidth of each demodulator.

Figure 5. Analog Reconstruction and Conditioning

Finally, the reconstructed demodulator data is passed through an analog multiplier with scaling factor that allows the user to program the overall maximum output level. A unipolar to bipolar converter provides a summing junction with reference voltage for the user to select unipolar or bipolar analog outputs, as well as positive-going or negative-going unipolar outputs.

### **Digital Data Combiner**

The digital output of each digital demodulator is available in two forms, parallel by subsystem or serial by individual demodulator. First, each demodulator individually outputs 16-bit serial data, with clock and most significant bit strobe on an output connector on each card. The outputs of all the demodulators in one subsystem may also be combined together using the combiner shown in Figure 1. This combined digital output provides 16-bit parallel data, with 8-bit channel ID, 24-bit time tag, and data clock. The format of the combiner output is set up by the DFD microcontroller and the output format can be displayed on the front panel. The DFD microcontroller calculates the most efficient output format using the different sampling rates for each channel. Individual digital outputs can be easily handled by common computer interfaces available at the data reduction facilities.

### SUMMARY

With the development of DSP algorithms and ASIC modules used in the DFD, the realization of a fully programmable, driftless FM digital demultiplexing data acquisition system has occurred. There is no longer a need to use antiquated plug-in analog FM demodulator systems or to use bandwidth restricted direct digital storage techniques for wide-band data acquisition measurements.

The Metraplex family of ASIC DSP modules can also be used for many other applications in the data acquisition and communication community. These technical building blocks can be used to create future DSP algorithm based instruments in the

filtering and sampling arena as well as providing different types of modulation and demodulation instruments for the test and telemetry community.

#### ACKNOWLEDGMENTS

Carl Smith was a key contributor to the overall conceptual design work described in this paper. The author appreciates the efforts of this individual as well as the other members of the project design team.

#### REFERENCES

1. DeFatta, David, et al, *Digital Signal Processing*, John Wiley & Sons, New York, 1988.

2. Sadr, R., et al, "Digital Carrier Demodulation for the DSN Advanced Receiver," *TDA Progress Report 42-93*, vol. Jan-March 1988, Jet Propulsion Laboratory, Pasadena, California, March 1990.